# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique Arrêté ministérial : 25 Mai 2016

Présentée par

# Fatma Jebali

Thèse dirigée par Frédéric Lang et codirigée par Radu Mateescu

préparée au sein d'Inria Grenoble Rhône-Alpes, du Laboratoire d'Informatique de Grenoble et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Formal Framework for Modelling and Verifying Globally Asynchronous Locally Synchronous Systems

Thèse soutenue publiquement le **12/09/2016**, devant le jury composé de :

#### **Monsieur Nicolas Halbwachs**

Vérimag, Président

# **Monsieur Alessandro Fantechi**

Université de Florence, Rapporteur

# **Madame Virginie Wiels**

ONERA, Rapporteur

# **Monsieur Jean-Pierre Talpin**

Inria Rennes, Examinateur

#### Monsieur Éric Jenn

IRT Saint-Éxupéry, Examinateur

# Monsieur Frédéric Lang

Inria Grenoble. Directeur de thèse

#### Monsieur Radu Mateescu

Inria Grenoble, Directeur de thèse

# Acknowledgements

I am deeply grateful to my first supervisor, Frédéric Lang, for his invaluable help and guidance during my PhD, shaping the way I do research while giving me freedom to pursue my own ideas, and for being a constant source of self-transcendence. I am also heartily thankful to my second supervisor, Radu Mateescu, for his kindness and his wise and enthusiastic counsel through the thought-provoking discussions we had. From Frédéric and Radu, I have gained an incredible amount of life and research knowledge; for that, I cannot thank them enough.

I am also grateful to my examiners, Nicolas Halbwachs, Alessandro Fantechi, Virginie Wiels, Jean-Pierre Talpin, and Eric Jenn for their thorough reading of my thesis and their constructive comments. Special thank goes to Eric for providing me with the AutoFlight Control System as a case study and for insightful encouragement from an industry perspective.

Many thanks are due to the rest of the Convecs team, Hubert Garavel, Wendeline Serwe, and Gwen Salaün, for providing such a stimulating and cheerful environment of research. I owe much to Hubert for his enthusiasm, wisdom, and support providing me with much-needed advice along the way. I warmly thank Jingyan Jourdan-Lu and Eric Léo, my office mates, for being such pleasant company and for making the Bluesky project a wonderful experience. Thanks also to my fellows: Raquel Oliveira for graciously hosting me in her office during many Sundays; Gianluca Barbon and Lina Marsso, who appeared at critical times, for their soft presence and support; Abderahman Kriouile for inspiring me to apply my work on avionics systems; as well as Rim Abid, Lakhdar Akroun, Hugues Evrard, Lina Ye, José Ignacio Requeno, Kaoutar Hafdi, Imad-Seddick Arrada, Ajay Muroor-Nadumane, Mohammad-Ali Tabikh, Sai Srikar Kasi, and Zhen Zhang. I am grateful to Myriam Etienne, the Convecs team assistant, for her kindness and her ability to find solutions in tedious administrative situations.

I also thank the people with whom I collaborated through the Bluesly project: Ioannis Parissis, Chriptophe Deleuze, and Mouna Tka from the LCIS lab; Jean-Baptiste Gnuing, Guillaume Marie, Jackie Launay, and Vincent List from Crouzet Automatismes (now InnoVista Sensors).

I met many nice friends during my PhD. Particular thanks are due to Ferdaouss, my first Grenoble's friend; Hassan and Fatma, for being a second family to me; Alia, for being a source of happiness; Kaoutar, for her contagious serenity; as well as Nashwa, Imen, Wided, Jamel, Sonia, and Rihab.

My family gave me endless love, patience, and support in every step of my life. I am eternally grateful to my mum, from whom I learned finding my strength in difficult times; my dad, from whom I learned seeking perfection in everything I do; as well as Mohamed and Rihab, for all the moments of fun we had together.

# Abstract

A GALS (*Globally Asynchronous*, *Locally Synchronous*) system consists of several synchronous components that evolve concurrently, each with its own pace, and communicate altogether asynchronously. This thesis proposes a formal modelling and verification framework dedicated to GALS systems, with a focus on the asynchronous behaviour.

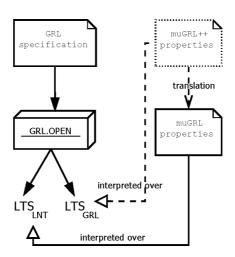

As a cornerstone of our framework, we have designed a formal language, named GRL (GALS Representation Language). GRL enables the behavioural specification of synchronous components, asynchronous communication, and constraints involving both component paces and the data carried by component inputs. To analyse GRL specifications, we took advantage of the CADP software toolbox for the verification of asynchronous concurrent processes, using state space exploration techniques. For this purpose, we have defined a translation from GRL to the LNT specification language supported by CADP. The translation has been implemented by a tool named GRL2LNT, thus enabling state spaces to be automatically derived from GRL specifications.

To enable the formal verification of GRL specifications, we have designed a property specification language, named muGRL, which is interpreted on GRL state spaces. The muGRL language is based on a set of patterns capturing properties of concurrent and GALS systems, which reduces the complexity of using full-fledged temporal logics. The semantics of muGRL are defined by a translation into the MCL temporal logic supported by CADP. Finally, we have illustrated how GRL, muGRL, and CADP can be applied to model and verify concrete GALS applications, including industrial case-studies.

# Résumé

Un système GALS (*Globalement Asynchrone*, *Localement Synchrone*) est un ensemble de composants synchrones qui évoluent en même temps, chacun à son propre rythme, et qui communiquent de manière asynchrone. Cette thèse propose un environnement formel de modélisation et de vérification dédié aux systèmes GALS, en se focalisant sur le comportement asynchrone.

Notre environnement s'appuie sur un langage formel que nous avons conçu, appelé GRL (GALS Representation Language). GRL permet la spécification comportementale des composants synchrones, de la communication asynchrone, et des contraintes sur les rythmes des composants ainsi que sur les valeurs que prennent les entrées des composants. Pour analyser les spécifications GRL, nous utilisons CADP, une boîte à outils logicielle permettant la vérification de processus concurrents asynchrones par des techniques d'exploration d'espaces d'états. Dans ce but, nous avons défini une traduction de GRL vers LNT, un langage de spécification supporté par CADP. La traduction est implémentée dans un outil appelé GRL2LNT, permettant ainsi la génération automatique d'espaces d'états à partir des spécifications GRL.

Pour permettre la vérification formelle des spécifications GRL, nous avons conçu un langage de propriétés, appelé muGRL, qui s'interprète sur les espaces d'états de GRL. Le langage muGRL est basé sur un ensemble de patrons qui capturent les propriétés des systèmes concurrents et des systèmes GALS, réduisant ainsi la complexité d'utiliser les logiques temporelles classiques. La sémantique de muGRL est définie par traduction vers MCL, le langage de logique temporelle fourni par CADP. Enfin, nous illustrons l'usage de GRL, muGRL et CADP pour modéliser et vérifier des applications GALS concrètes, comprenant des études de cas industrielles.

# Contents

| A                | Acknowledgements |             |                                                            |              |  |

|------------------|------------------|-------------|------------------------------------------------------------|--------------|--|

| $\mathbf{A}$     | bstra            | ct (Er      | nglish/Français)                                           | $\mathbf{v}$ |  |

| $\mathbf{C}_{0}$ | ontei            | $_{ m nts}$ |                                                            | vii          |  |

| 1                | Intr             | oduct       | ion                                                        | 1            |  |

| 2                | Bac              | kgrou       | nd and State of the Art                                    | 8            |  |

|                  | 2.1              | React       | ive systems                                                | 8            |  |

|                  |                  | 2.1.1       | Formal models for reactive systems                         | 9            |  |

|                  |                  | 2.1.2       | Formal verification of reactive systems                    | 11           |  |

|                  | 2.2              | The s       | ynchronous approach                                        | 13           |  |

|                  |                  | 2.2.1       | Synchronous languages                                      | 13           |  |

|                  |                  | 2.2.2       | Functional verification                                    | 15           |  |

|                  | 2.3              | The a       | synchronous approach                                       | 15           |  |

|                  |                  | 2.3.1       | Communication models                                       | 16           |  |

|                  |                  | 2.3.2       | Functional verification                                    | 17           |  |

|                  | 2.4              | The C       | CADP toolbox for the verification of asynchronous systems  |              |  |

|                  |                  | 2.4.1       | Labelled Transition Systems (LTS)                          | 18           |  |

|                  |                  | 2.4.2       | The LNT language                                           | 20           |  |

|                  |                  | 2.4.3       | The MCL language                                           |              |  |

|                  | 2.5              | Globa       | lly Asynchronous Locally Synchronous (GALS) systems        |              |  |

|                  |                  | 2.5.1       | GALS systems in synchronous languages and dedicated tools  |              |  |

|                  |                  | 2.5.2       | GALS systems in asynchronous languages and dedicated tools | 27           |  |

| 3                | The              | GRL         | Language for GALS Behavioural Description                  | 29           |  |

|                  | 3.1              | A GA        | LS example                                                 | 29           |  |

|                  | 3.2              | Overv       | iew of GRL                                                 | 30           |  |

|                  |                  | 3.2.1       | Modules                                                    | 30           |  |

|                  |                  | 3.2.2       | Synchronous blocks                                         | 32           |  |

|                  |                  | 3.2.3       | Asynchronous composition of blocks                         | 32           |  |

|                  | 3.3              | Basic       | GRL                                                        | 34           |  |

# Contents

|   |     | 3.3.1         | Type definitions                                         |

|---|-----|---------------|----------------------------------------------------------|

|   |     | 3.3.2         | Expressions                                              |

|   |     | 3.3.3         | Statements                                               |

|   |     | 3.3.4         | Global constant definitions                              |

|   | 3.4 |               | s                                                        |

|   | 5.4 | 3.4.1         | Block definition                                         |

|   |     | 3.4.1         | Subblock composition                                     |

|   |     | 3.4.3         | Discussion and related work                              |

|   | 3.5 |               | onments                                                  |

|   | 5.5 | 3.5.1         | Data constraints                                         |

|   |     | 3.5.1 $3.5.2$ | Activation constraints                                   |

|   |     | 3.5.2         | Combining data and activation constraints                |

|   | 3.6 |               | ms                                                       |

|   | 3.0 |               | ns                                                       |

|   | 3.1 | 3.7.1         | System definition                                        |

|   |     | 3.7.2         | ·                                                        |

|   |     | 3.1.2         | Discussion and related work                              |

| 4 | For | mal Dy        | ynamic Semantics of GRL 56                               |

|   | 4.1 | Prelim        | ninaries                                                 |

|   |     | 4.1.1         | Stores                                                   |

|   |     | 4.1.2         | Stacks                                                   |

|   |     | 4.1.3         | Memories                                                 |

|   |     | 4.1.4         | LTSs of GRL systems                                      |

|   |     | 4.1.5         | Structural Operational Semantics (SOS) 60                |

|   | 4.2 | Expres        | ssions                                                   |

|   | 4.3 | Staten        | nents                                                    |

|   |     | 4.3.1         | Basic statements                                         |

|   |     | 4.3.2         | Signals                                                  |

|   | 4.4 | Store         | construction at component invocation                     |

|   |     | 4.4.1         | Auxiliary functions                                      |

|   |     | 4.4.2         | Global store                                             |

|   |     | 4.4.3         | Store and memory construction at component invocation 69 |

|   | 4.5 | Blocks        | s                                                        |

|   | 4.6 | Enviro        | onments and mediums                                      |

|   | 4.7 | System        | ns                                                       |

|   |     | 4.7.1         | Sets and auxiliary functions                             |

|   |     | 4.7.2         | Semantics of systems                                     |

|   |     | 4.7.3         | Relation with existing work                              |

| 5 | Two | nelatia       | n from GRL into LNT                                      |

| J | 5.1 |               | iew of the translation                                   |

|   | 5.1 |               | ation of variables, types, expressions, and statements   |

|   | 5.3 |               | ation of variables, types, expressions, and statements   |

|   | 0.0 | TIALISI       |                                                          |

|   | 5.4  | Transl  | lation of variable declarations, parameters, and internal states .  | 84         |

|---|------|---------|---------------------------------------------------------------------|------------|

|   |      | 5.4.1   | Preliminaries                                                       | 84         |

|   |      | 5.4.2   | Translation of variable declarations and activation parameters .    | 86         |

|   |      | 5.4.3   | Translation of actual parameters                                    | 87         |

|   |      | 5.4.4   | Translation of actual channels                                      | 88         |

|   |      | 5.4.5   | Construction of the internal state                                  | 91         |

|   | 5.5  | Transl  | lation of blocks                                                    | 93         |

|   |      | 5.5.1   | Block definition                                                    | 93         |

|   |      | 5.5.2   | Subblock aliasing and invocation                                    | 96         |

|   |      | 5.5.3   | Highest-level block aliasing and invocation                         | 98         |

|   | 5.6  | Transl  | lation of environments and mediums                                  | 102        |

|   |      | 5.6.1   | Signals                                                             | 103        |

|   |      | 5.6.2   | Environments                                                        | 103        |

|   |      | 5.6.3   | Mediums                                                             | 106        |

|   | 5.7  | Transl  | lation of systems                                                   | 106        |

|   |      | 5.7.1   | Sets and auxiliary functions                                        | 106        |

|   |      | 5.7.2   | Translation function                                                | 108        |

|   | 5.8  | Tool s  | support                                                             | 113        |

|   | 5.9  | LTSs o  | of the translation vs. LTSs of GRL semantics                        | 114        |

|   | 5.10 | Comp    | arison with related work                                            | 115        |

|   | 5.11 | Conclu  | usion                                                               | 116        |

| 6 | The  | muG     | RL Language for GALS Property Specification                         | 117        |

| Ū | 6.1  |         | iew of muGRL                                                        |            |

|   | 6.2  |         | formulas                                                            |            |

|   | 6.3  |         | n formulas                                                          |            |

|   | 6.4  |         | ar formulas                                                         |            |

|   | 6.5  | _       | al property patterns                                                |            |

|   |      |         | Patterns for safety properties                                      |            |

|   |      | 6.5.2   | Patterns for liveness properties                                    |            |

|   |      | 6.5.3   | Patterns for fairness properties                                    |            |

|   |      | 6.5.4   | Translation into MCL                                                |            |

|   | 6.6  |         | ock, livelock, and instability                                      |            |

|   |      | 6.6.1   | Deadlock                                                            |            |

|   |      | 6.6.2   | Livelock                                                            |            |

|   |      | 6.6.3   | Instability                                                         |            |

|   | 6.7  | Discre  | ete real-time properties                                            |            |

|   | 6.8  | Concl   |                                                                     |            |

| 7 | F    | mal N/I | adelling and Varification of CAIS Applications                      | 1 1 1      |

| 1 | 7.1  |         | odelling and Verification of GALS Applications -synchronous systems | 144<br>144 |

|   | 1.1  | 7.1.1   | Primary implementation                                              |            |

|   |      | 1.1.1   | - 1 1 1 1 1 1 (A) V 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1             | 171        |

|   |      |         | Refined implementation                                              |            |

# Contents

|              |            | 7.1.3   | Discussion                                     | . 150 |

|--------------|------------|---------|------------------------------------------------|-------|

|              | 7.2        | Detern  | ninistic GALS systems                          | . 150 |

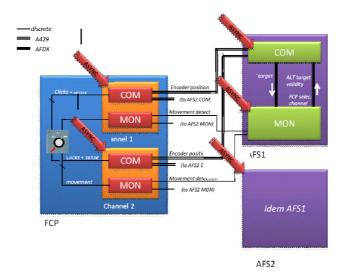

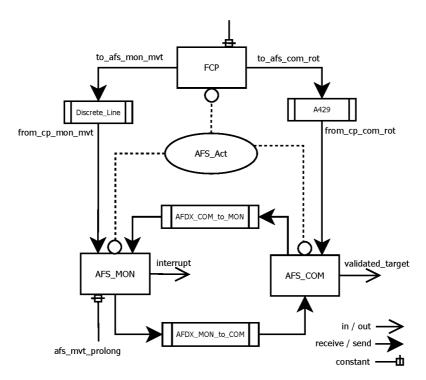

|              | 7.3        | AutoF   | light Control System (AFCS)                    | . 151 |

|              |            | 7.3.1   | Overview of the system                         | . 151 |

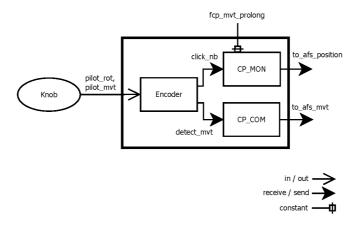

|              |            | 7.3.2   | Modelling and verifying component FCP          | . 153 |

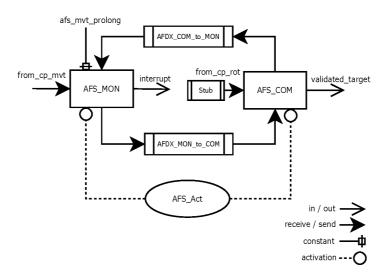

|              |            | 7.3.3   | Modelling and verifying component AFS          | . 155 |

|              |            | 7.3.4   | Modelling and verifying the AFCS system        | . 159 |

|              |            | 7.3.5   | Discussion                                     | . 164 |

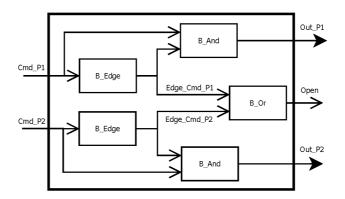

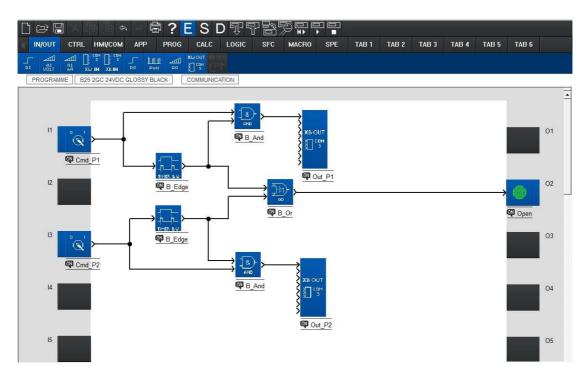

|              | 7.4        | Netwo   | rks of Programmable Logic Controllers          | . 164 |

|              |            | 7.4.1   | The car park application                       | . 165 |

|              |            | 7.4.2   | Industrial use of GRL                          | . 167 |

| 0            | <b>C</b>   | clusior | _                                              | 100   |

| 8            | Con        | ciusioi | 1                                              | 168   |

| $\mathbf{A}$ | The        | GRL     | Model and SVL Verification Scripts of the AFCS | 172   |

|              | A.1        | The G   | RL model                                       | . 172 |

|              |            | A.1.1   | Global constants                               | . 172 |

|              |            | A.1.2   | Component FCP                                  | . 172 |

|              |            | A.1.3   | Component AFS                                  | . 174 |

|              |            | A.1.4   | System AFCS                                    | . 180 |

|              | A.2        | The S   | VL verification script                         | . 183 |

|              |            | A.2.1   | Generation and verification script             | . 183 |

|              |            | A.2.2   | Property patterns                              | . 192 |

| В            | The        | CRI.    | Model of the Car Park Application              | 194   |

| ט            | B.1        |         | constants                                      |       |

|              | B.2        |         | ocks modelling function blocks                 |       |

|              | B.3        |         | et-level blocks modelling PLCs                 |       |

|              | Б.3<br>В.4 | 0       | onments                                        |       |

|              | B.5        |         | ms                                             |       |

|              | B.6        |         | ns                                             |       |

|              | ט.ט        | System  | 15                                             | . 404 |

# Chapter 1

# Introduction

Constructing correct software and hardware systems is challenging. System quality relies not only on good performance such as processing capacity, but also on the absence of errors. For hardware systems, defects may have severe economic consequences. For software used in safety-critical systems, a simple bug can have disastrous human consequences. Concurrent systems, which are composed of several (hardware or software) components possibly interacting with each other, are particularly vulnerable to errors. The number of possible concurrency errors (that is, errors due to wrong ordering of concurrent events) is exponential in the number of the concurrent components. Hence, a major goal when constructing concurrent systems is their correctness despite their complexity.

Formal methods provide languages, techniques, and tools to establish system correctness. The mathematical rigour of formal methods favours an early integration of verification in the design process. For example, they have been applied in the certification of avionics software systems [DO-11, MLD+13] and railway systems [FFG14].

Model-based verification builds on models describing the system behaviour, i.e., what the system may do during its execution, by means of events, in an abstract and precise way. In practice, models are usually derived from high-level formalisms endowed with precise semantics. Correctness properties, also written in high-level formalisms, can be checked over models. The efficiency of the verification task relies on the adequacy of the high-level formalisms with regards to the subtleties of intended systems.

# Context

According to the nature of component composition and communication, concurrent systems can be classified into *synchronous* and *asynchronous*; for each class, well-adapted formalisms are tailored to capture system behaviour.

Synchronous concurrent systems are composed of several components running in lockstep

fashion and sharing a global clock. For these systems, synchronous languages, among which *Esterel* [BG92], *Lustre* [HCRP91], and *Signal* [LGGLBLM91], are appropriate modelling formalisms. They rely on the *synchrony assumptions*: a system is seen as a deterministic and infinite loop, whose iterations represent the clock ticks; within each loop iteration, computations and data-flow communication are assumed to occur in zero-delay. The synchrony assumptions make the modelling and verification tasks easy.

Asynchronous concurrent systems are composed of several components running independently without a global clock and interacting with each other. For these systems, process algebras, among which *CCS* [Mil89], *CSP* [Hoa85], and *LOTOS* [BB87], are appropriate modelling formalisms. They are equipped with built-in operators for asynchronous parallel composition; they provide abstraction means (e.g., nondeterminism); and they have equivalence relations to efficiently and precisely compare systems.

Correctness properties of concurrent systems include the absence of undesirable situations and the succession of events in time, which can be arbitrarily far from each other. To express properties,  $temporal\ logics$ , among which  $LTL\ [Pnu77]$  and  $CTL\ [EC82]$ , are powerful means. They consist of a small set of temporal operators expressing the logical precedence of events over time.

This thesis is about formally modelling and verifying GALS (Globally Asynchronous, Locally Synchronous) systems [Cha84], which are a class of concurrent systems. A GALS system is composed of synchronous components running in asynchronous concurrency without sharing their clocks. Communication between components is also asynchronous, i.e., message exchange may take an arbitrary amount of time. For example, in a flight control system, individual components are designed to run synchronously, but the distributed nature of the global system introduces asynchrony. Other GALS instances include networks-on-chip and distributed PLCs (Programmable Logic Controllers).

In the general case, a GALS system may have arbitrary complexity. No assumption can be made on clock synchronisation and component periods, nor on asynchronous communication media and their latency. Each GALS instance induces its own assumptions. In particular, although synchronous components are generally *deterministic*, the absence of a shared clock may introduce *nondeterminism*. Another source of nondeterminism is unreliable communication media along which messages can be delayed, lost, duplicated, or reordered. This makes system evolution unpredictable and unreproducible, entailing a need for formal verification.

# Motivation

The correctness of GALS systems relies on combining the verification approach for synchronous systems and the one for asynchronous systems. Each approach, applied individually, is unable to capture the behavioural subtleties for which the other approach is devised. Languages and tools for synchronous systems are deterministic by nature, thus

unadapted to analyse nondeterminism and asynchronous concurrency. Languages and tools for asynchronous systems lack built-in constructs dedicated to address the pure synchrony assumptions.

We have identified a relative lack of approaches dealing with asynchronous concurrency in existing design processes of GALS systems, compared to the intensive use of approaches dealing with synchrony. This lack is manifold. On the one hand, the GALS paradigm takes its roots in the industries that already integrated synchronous languages and corresponding tools in their development process. Consequently, the focus has been shifted towards pushing the limits of synchronous languages and tools to accommodate GALS behaviours. On the other hand, synchrony is easier to master than asynchrony, owing to the zero-delay assumption and determinism, which makes systems easy to design and debug. Contrarily, asynchronous concurrent languages and temporal logics require a substantial learning effort, which may discourage potential users. Last, the behaviour of GALS systems involves asynchronous concurrency and data handling, which are two major causes of combinatorial explosion (in the possible behaviours). Additional effort should be put to make careful modelling decisions and to choose adequate algorithmic approaches, e.g., compositional verification, to face combinatorial explosion.

To alleviate the use of verification tools for asynchronous systems, one needs to introduce DSLs (*Domain Specific Languages*) [vDKV00]. GALS-specific languages serve as intermediate format mapping GALS systems, whose synchronous components are possibly modelled using synchronous languages, to verification tools for asynchronous systems. Due to the different semantics and abstraction level, a direct connection from (synchronous) design languages to asynchronous languages could be complex. Instead, performing the translation in several steps reduces that complexity and enhances the connection modularity.

As regards behavioural modelling, a DSL should provide a clear distinction between synchronous components and the asynchronous ones defining their asynchronous composition and communication. Such a distinction enables to combine of verification tools for synchronous systems and those for asynchronous systems to address separately the DSL synchronous and asynchronous components. For synchronous components, possibly obtained from translation of existing synchronous languages, the DSL can be a (minimal) language used as target of back-end compilers for synchronous languages. To ensure the practical usability of the DSL, it should enable a natural description of relevant aspects of GALS behaviour, in a way close to the end-user intuition and expectation.

As regards correctness properties, their formulation in temporal logic can be difficult and error-prone, even for users familiar with formal methods and verification. One needs a formalism tailored to capture GALS behaviour and enabling a *concise* and *natural* expression of properties.

### Contributions

This thesis proposes a formal framework to analyse GALS systems focusing on their asynchronous behaviour. In this respect, we take advantage of the CADP software toolbox [GLMS13] for the verification of asynchronous concurrent processes, using state space exploration techniques.

As a cornerstone of our framework, we have designed a formal language, named GRL (*GALS Representation Language*) [JLM14a]. GRL aims at offering a concise and modular description for the behaviour of GALS systems. Both traits of synchronous programming (determinism, atomicity) and process algebra (nondeterminism, asynchronous concurrency) are combined in one unified language, while keeping homogeneous syntax and semantics. GRL builds upon the following three core constructs:

**Blocks** denote the synchronous part of GRL, in which the synchrony assumptions are built-in. They provide a number of basic constructs to which synchronous language constructs can be translated.

**Mediums** denote asynchronous components describing communication media. They are provided with enough expressiveness to model general asynchronous communication, with different buffering mechanisms, including unreliable ones.

Environments denote asynchronous components abstracting the external environment of blocks. Two kinds of constraints with different abstraction levels are considered. Data constraints enable to express complex properties on the data carried by block inputs. Activation constraints enable to control the execution of blocks, such as relations between block paces, priorities, or failure. Furthermore, it is possible to combine both kinds of constraints for enhanced usage, such as complex test case scenarios.

All-in-one, GRL is intended to be sufficiently expressive and concise to model complex GALS systems, which is an originality compared to state-of-the-art approaches.

We formalise the semantics of GRL, using structural operational semantics (SOS) rules, in terms of lower-level models, i.e., state spaces. This enables rigorous specification of GRL programs and paves the way for formal analysis. State spaces underlying GRL are concise, exploiting the GALS assumptions such as the atomicity of synchronous components. This enhances the efficiency of verification. Data and activation constraints would also contribute to face combinatorial explosion.

After formally defining the syntax and semantics of GRL, we address its compilation into state spaces. For this purpose, we design a translation from GRL into LNT [CCG<sup>+</sup>16], the most recent specification language supported by CADP. LNT is a general-purpose language implementing concurrency theory results and equipped with state space generators. We formalise the translation function from GRL into LNT, which is fully implemented in a tool named GRL2LNT<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The GRL2LNT tool has been implemented, mainly not by the author, in the framework of an

To analyse GRL specifications, we exploit the MCL language, a full-fledged temporal logic supported by CADP. To leverage the expressiveness of MCL while reducing its complexity of usage, we design a property description language, named muGRL. The muGRL language builds upon a pattern system, following the general-purpose approach [DAC99], which is also an originality of our approach. Patterns are high-level templates that capture frequently encountered situations in GALS applications, such as component halting and idleness, and are translatable into temporal logics. The interpretation models of muGRL are the state spaces generated by translating GRL specifications into LNT. The muGRL semantics are defined by a translation into MCL. As such, muGRL is intended to disseminate temporal logic power to potential GALS designers.

Last, we experiment our approach on concrete GALS applications, issued from academia and industry. This reinforces our conviction that our approach can address a large spectrum of GALS systems, ranging from deterministic applications to ones involving arbitrary nondeterminism.

#### Thesis Outline

The remainder of this thesis is structured as follows. Chapter 2 surveys the state-of-the-art concerning the formal modelling and verification of concurrent and GALS systems. Chapter 3 constitutes a tutorial for the GRL language. It presents the formal syntax of each GRL construct, its intuitive semantics, along with some illustrations. Chapter 4 presents the formal dynamic semantics of GRL. It details the structural operational semantic rules for the language constructs, stressing on the behavioural ones. Chapter 5 presents the formal translation functions from GRL into LNT. Examples are given for most of the functions, to enhance the readability and ease the comprehension. Chapter 6 constitutes a tutorial for the muGRL language. Chapter 7 shows the way GRL and muGRL can be applicable to concrete GALS applications. It also briefly reports a primary industrial use of GRL. Chapter 8 concludes and offers some thoughts on extensions to this work.

Parts of this manuscript have been published in conference proceedings and journals. The article [JLM14a] presents an overview of an earlier version of GRL, the complete and formal definition of GRL being available in an 82-pages research report [JLM14b]. Since then, we have revised and enhanced the syntax of the language. The article [JLM16] presents the latest version of GRL, including the material of chapters 3 and 4 as well as an informal presentation of chapter 5.

industrial project, named *Bluesky*, of the Minalogic French competitiveness cluster (www.minalogic.com/fr/projet/bluesky). The project addresses the design and validation of networks of PLCs (*Programmable Logic Controllers*).

# **Notations**

We introduce some mathematical concepts and conventions used in this thesis.

# General notations

A set is an ordered collection of objects, called its elements. The following operators over sets are used:

| Symbol                          | Meaning                                                                              |  |

|---------------------------------|--------------------------------------------------------------------------------------|--|

| $a_1,\ldots,a_n$                | possibly empty finite sequence of elements of length n                               |  |

| $a_0,\ldots,a_n$                | non-empty finite sequence of elements of length n+1 ( $\epsilon$ if empty)           |  |

| $\{a_1,\ldots,a_n\}$            | possibly empty set of elements $a_1, \ldots, a_n$ of size n                          |  |

| $\{a_0,\ldots,a_n\}$            | non-empty set of elements $a_0, \ldots, a_n$ of size n+1 ({} if empty)               |  |

| $\langle a_1,\ldots,a_n\rangle$ | possibly empty list of elements $a_1, \ldots, a_n$ of size n ( $\epsilon$ if empty)  |  |

| $\langle a_0,\ldots,a_n\rangle$ | non-empty list of elements $a_0, \ldots, a_n$ of size $n+1$                          |  |

| $a \in A$                       | a is an element of the set $A$                                                       |  |

| $A \subseteq B$                 | A is a subset of the set $B$                                                         |  |

| $a \in A \mid P(a)\}$           | the set which contains only elements of $A$ satisfying property $P$                  |  |

| $A \times B$                    | the set of all ordered pairs $(a,b)$ where $a\in A$ and $b\in B$ (Cartesian product) |  |

| 1 <i>n</i>                      | interval whose elements range from 1 to n                                            |  |

We use the operator ++ for list concatenation. For a set of lists  $\{\mathcal{L}_0, ..., \mathcal{L}_n\}$ , we write  $\underset{i \in 0..n}{++} \mathcal{L}_i$  as abbreviation for  $\mathcal{L}_0$ ++...++ $\mathcal{L}_n$ .

The following logical operators are used:

| Symbol        | Meaning     |

|---------------|-------------|

| _             | negation    |

| ^             | conjunction |

| V             | disjunction |

| $\Rightarrow$ | implication |

For a set of elements  $\{a_0, \ldots, a_n\}$ , we write  $\bigwedge_{i \in 0 \ldots n} a_i$  and  $\bigvee_{i \in 0 \ldots n} a_i$  as abbreviation for  $a_0 \wedge \ldots \wedge a_n$  and  $a_0 \vee \ldots \vee a_n$ , respectively.

# Syntactic description

This document defines and references several languages. Grammars of languages are context-free. Syntactic definitions are presented in *Extended Backus-Naur Form* [Sta96], i.e., as a set of so-called *productions*. Each production has the form " $\chi := \xi$ ", where  $\chi$  is a non-terminal symbol defined by the meta-expression  $\xi$ , which consists of non-terminal symbols and terminal symbols composed using the following meta-operators:

| Notation           | Operation                 | Description                                        |

|--------------------|---------------------------|----------------------------------------------------|

| $(\xi_{\theta})$   | bracketing                | $\xi_{\theta}$                                     |

| $[\xi_{\theta}]$   | option                    | $\xi_{\theta}$ or nothing                          |

| $\xi_0*$           | possibly empty repetition | $\xi_{\theta}$ , zero, one, or several occurrences |

| $\xi_0+$           | non-empty repetition      | $\xi_{\theta}$ , one, or several occurrences       |

| $\xi_1 \xi_2$      | concatenation             | $\xi_1$ followed by $\xi_2$                        |

| $\xi_1 \mid \xi_2$ | alternative               | $\xi_1$ or $\xi_2$                                 |

Additionally, the following conventions are used:

- Non-terminal symbols and generic terminal symbols are written in italics and their occurrences can be distinguished using subscripts.

- The terminal symbol are either keywords written in bold font or key symbols are written in teletype font. For example, "[]", "()", and "|" denote terminal symbols distinct from the meta-operators "[]", "()", and "|".

# Chapter 2

# Background and State of the Art

A GALS system combines characteristics of synchronous and asynchronous systems, which both belong to the class of reactive systems [HP85, Ber89, Hal10]. These are systems in permanent interaction with the outside world. In this chapter, we first introduce reactive systems. We then present the synchronous and asynchronous approach to formally model and verify reactive systems. We focus in particular on the use of the CADP toolbox for verifying asynchronous concurrent systems. Finally, we present existing approaches to the formal analysis of GALS systems.

# 2.1 Reactive systems

Hardware and software programs and systems interact with their environment, that is, the outside world within which they evolve. They can receive inputs from their environment and produce the appropriate outputs, which have effect on their environment. A program is said transformational if it receives inputs and terminates after producing outputs. Usually, the same inputs induce the same outputs, in which case the program is said deterministic. A transformational program can be described as a mathematical function that transforms inputs into outputs. Examples are compilers and optimisation algorithms.

Not all systems and programs intend to yield a final result. A system might well aim to maintain some interaction with its environment. The environment continuously prompts the system by providing it with inputs and the system reacts by producing outputs. Examples are operating systems, communication protocols, and database management systems. Such systems are called *reactive*, and a computation of outputs from inputs is called a *reaction*. Reactive systems may be subject to strict timing constraints, in which case they are referred to as *real-time systems*. In a railroad-crossing control system, it is crucial to block vehicle crossing as soon as a train approach is detected.

Concurrency is inherent in reactive systems. First, a reactive system together with its

environment form a concurrent system. Second, reactive systems are often decomposed into several *concurrent components* or tasks that operate simultaneously. Concurrent components are usually reactive themselves; they interact with their environment and potentially with each other.

Nondeterminism is usually introduced by concurrency. Two different copies of the same concurrent system are likely to operate differently, while given exactly the same inputs. An example is when several components compete to acquire a resource and the resource operates depending on which component has won the race.

Implementations of concurrent components are multiples. They may run *sequentially*, a component finishing before the next starts, or *in parallel*, all components evolving at the same time. Parallel components may run over a multi-core processor or a multi-processor machine, to speed up computations. They may also run over spatially distant machines exchanging data through a network, in which case components are called *distributed*.

Reactive systems cannot be described as mathematical functions taking inputs and producing outputs, since they run continuously without necessarily terminating, they Rather, they are described in terms of a set of infinite sequences of states and transitions (or actions) between states. Such infinite sequences are usually called executions. We define the behaviour of a system as the set of its possible executions. The behaviour of a concurrent system is specified in terms of the behaviours of its components. Hence, it is essential to understand the way states corresponding to component behaviours can be combined and the consequences of such combinations.

To establish the correctness of reactive systems, one needs appropriate behavioural models on which formal verification can be performed using dedicated algorithms. An appropriate behavioural model should provide an abstract and modular description of both a reactive system, its environment, and its concurrent components. The model should provide a description of the interaction between the system and its environment as well as between concurrent components. Last but not least, the model should provide a suitable abstraction of time. In this thesis, we consider a discrete representation. Time is an infinite series of discrete instants, which can (or not) be equally separated. When discrete instants are not equally separated, we are considering logical time.

# 2.1.1 Formal models for reactive systems

This section surveys some existing formal models for reactive systems. In particular, we focus on *transition systems*, in which a system is modelled in terms of states and actions. Existing models differ in the way they abstract a system behaviour, each emphasising certain aspects disregarding the others. We classify models according to the following three dichotomies, which we believe adequate to the comprehension of this thesis.

Linear-time versus branching-time [Lam80] In linear-time models, the system behaviour is expressed as the set of its possible executions, i.e., linear sequences of states and actions. This model is well suited to deterministic systems since at each moment in time, the system has a unique future. In branching-time models, the system behaviour is expressed as *computation trees* that structure the possible executions. This model is adequate to capture nondeterministic behaviours, since at each moment in time, the system can have several futures. The two models differ in the way they deal with nondeterminism. As an illustration, consider two coffee machines [Hoa85]. The first machine, once a coin is inserted, gives the user a choice between coffee and tea, and serves the user's choice. The second machine, once a coin is inserted, makes internally a nondeterministic choice, and serves either coffee or tea. Both machines have the same set of possible executions {coin, coffee} or {coin, tea}. The branching-time view distinguishes the difference between the two machines while the linear-time view does not.

Action-based versus state-based [DNV90] In the action-based setting, the contents of states is abstracted away. The evolution of the system behaviour is encoded in actions. Actions correspond to the interaction of the system with its environment, i.e., inputs received and outputs sent by the system, as well as internal transitions performed by the system. Examples of action-based representations include labelled transition systems [Par81], Petri-nets [Pet62], and I/O automata [LT89]. The state-based setting is the dual of the action-based one, from a theoretical point of view. The evolution of the system behaviour is encoded inside states, by means of variables and other information stored in memory. Only the internal contents of states can be observed. Examples of state-based representations include Kripke structures [Kri63]. In practice, the action-based representation can be seen as a "black box" view of a system and state-based models as "white box" one.

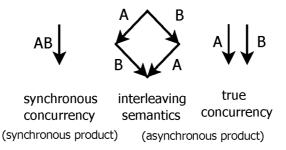

Synchronous versus asynchronous concurrency Concurrent components can be composed either in a *synchronous* or in an *asynchronous* way. Synchronous concurrent components evolve in a lockstep fashion, cadenced by a single central clock. Each clock pulse prompts all concurrent components to react. The conjunction of component actions at the same clock pulse constitutes an action of the whole system. This concurrency model is mainly supported by synchronous languages, such as *Esterel* [BG92], *Lustre* [HCRP91], and *Signal* [LGGLBLM91].

Asynchronous concurrent components evolve independently without clock sharing. A first model for asynchronous concurrency is the so-called *interleaving semantics* [Mil89]. In this model, concurrency between components is reduced to a nondeterminism choice between the possible sequences of the component actions. This model of concurrency is mainly supported by process algebras, such as CCS [Mil89], CSP [Hoa85], ACP [BK85], and LOTOS [BB87].

Another model for asynchronous concurrency is the so-called *true-concurrency* [Mon92], also called *non-interleaving model*. In this model, concurrency is a primitive notion clearly distinguishable from sequential nondeterminism. The system behaviour is represented in terms of the causal relations among actions performed by components; two actions are concurrent if they are not causally related. This model of concurrency is mainly supported by Petri-nets and Kahn-nets [Kah74].

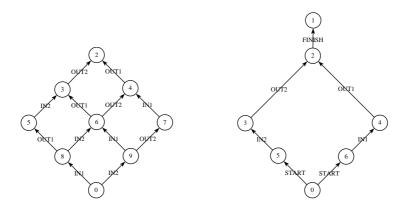

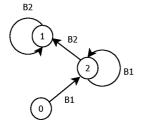

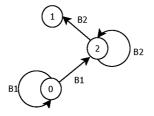

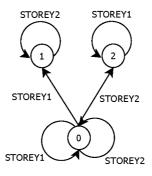

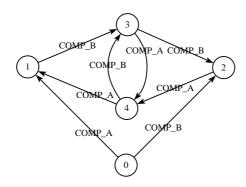

An illustration of the three models of concurrency (in an action-based setting) is given in Figure 2.1. Actions A and B are concurrent. The synchronous composition of actions A and B results in one action labelled AB. The interleaving semantics expresses that either action A occurs followed by action B or action B occurs followed by action A. The true-concurrency model can be understood as a system with two initial states, each with an outgoing transition, since actions A and B are not causally related.

Figure 2.1: Models of concurrency in an action-based setting

#### 2.1.2 Formal verification of reactive systems

To perform formal verification, one needs, in addition to a *model* describing all potential behaviours of the system, to describe the set of *properties* that must hold on the system. The verification problem consists in proving (automatically) that the model satisfies the properties. We briefly introduce the common formal verification approaches:

- Static analysis consists in verifying programs, without executing them, relying on the semantics of the language in which programs are written. The abstract interpretation technique [CC77] consists in abstracting the model to a smaller one, in such a way that if the desired property holds on the abstracted model, it must hold on the original one. Among the static analysers based on abstract interpretation, we cite Astrée [CCF+05] and Verasco [JLB+15]. Abstract interpretation is used extensively in transformational systems such as in compiler optimisation and sequential program verification. While being an automated technique, abstract interpretation cannot achieve 100% precision in the general case.

- Theorem proving consists in modelling the system as a set of mathematical definitions. The desired properties of the system are derived as theorems that stem

from those definitions. Proofs can be constructed either by hand or by using automatic theorem provers and interactive proof checkers. Although it cannot be fully automated, theorem proving is assisted by powerful proof assistant, among which Coq [FHB<sup>+</sup>97] and Isabelle [Pau89]. Theorem proving techniques are particularly useful in the case of general infinite-state reactive systems, e.g., systems containing unbounded data structures. They have been used in the context of reactive and real-time systems, but less for distributed concurrent systems.

• Model checking consists in modelling the system as a (finite) transition system that describes all the possible executions of the system. The desired properties of the system can be described by reasoning about the temporal ordering of events<sup>1</sup>. Temporal logic formalisms have been introduced in the late seventies [Pnu77] for this purpose. A temporal logic is a set of operators, expressing the logical precedence either between states (state-based temporal logic) or between actions (action-based temporal logic). Additionally, temporal logics can be interpreted either on linear-time models, by specifying properties of individual execution sequences, or on branching-time models, by taking into account the branching structure of the state space. According to these two dichotomies, a lot of formalisms have been proposed. The following table shows the most representative ones.

| linear-time | branching-time | linear- and branching-time |

|-------------|----------------|----------------------------|

| LTL [Pnu77] | CTL [EC82]     | CTL* [EH86]                |

| ALTL [GM03] | ACTL [DFGR93]  | ACTL* [DNV90]              |

Given a state space and a property, the *model checking* problem [CGP00] consists in determining whether the state space satisfies the property or not. If the property does not hold on the state space, it is desirable to obtain a diagnostic (or counterexample) showing an undesirable behaviour present in the state space. This problem is solved by model checking algorithms, which traverse the state space and halt as soon as the truth value of the property has been determined. State space traversing techniques are typically grouped in two classes:

- enumerative techniques consider each state of the system separately

- symbolic techniques manipulate sets of states represented using either decision diagrams or logical formulas. The satisfiability of those representations is determined using SAT and SMT solvers.

Another way to describe nontrivial properties is *equivalence checking*. It consists in expressing a specification of the system in terms of input/output relations, then deriving whether the system and its specification are behaviourally equivalent.

It is common to combine several verification techniques (e.g. [Hun93, HS96, Amj04]) to exploit their best capabilities while reducing their shortcomings. In this thesis, we focus

<sup>&</sup>lt;sup>1</sup>The term "temporal ordering" should not be confused with the real-time aspect of reactive systems. The meaning here is the relative order of events, time being abstracted.

on the model checking technique, adequate to address the subtleties of concurrency.

While transition systems are adequate to model concurrent components interacting with each other, building them manually is complex and error-prone. Moreover, the slightest modification in the specification may involve drastic changes in the structure of the transition system, making it cumbersome to debug and modify. For these reasons, transition systems are often derived from descriptions written in high-level formalisms, by automatic translation. There are several high-level formalisms, each emphasising a specific class of systems.

In the sequel, we present the synchronous approach, well-adapted to deal with sequential and parallel systems such as hardware circuit designs and embedded systems. We also present the asynchronous approach, well-adapted to deal with parallel and distributed systems such as telecommunication protocols and distributed software.

# 2.2 The synchronous approach

A reactive system is synchronous if it reacts instantaneously to its environment and has a deterministic behaviour.

A reaction is assumed instantaneous if on the arrival of some inputs from the environment, a system reacts fast enough to produce the corresponding outputs, before the arrival of the next inputs. Hence, the system behaves as an infinite loop, called *synchronous loop*, each iteration corresponding to a reaction. In the remainder of this thesis, we will use the terms *step* to denote the reaction of a synchronous system and *activation* its ability to perform a step at a specific logical instant.

Synchronous concurrent components composing the system are cadenced by its synchronous loop. Component (micro-) steps may be *idle*, i.e., their inputs and outputs keep the same values as in the previous step. Messages emitted by components are received by other components in the same step; such communication is called *instant broadcast*. Instantaneous computations and communication are usually called *zero-delay* (or *synchrony*) assumptions.

A consequence of the synchrony assumptions is the determinism of the synchronous loop: given the same initial state and sequence of inputs, the same sequence of outputs will be produced. Determinism is desirable in safety-critical environments, in which a simple bug can have extreme consequences. Another consequence of the synchrony assumptions is the potential presence of temporal paradoxes, called *causality problems*. Examples include instantaneous dependencies between inputs and outputs.

#### 2.2.1 Synchronous languages

Theoretical foundations can (a priori) be traced back to R. Milner's synchronous process algebra SCCS (Synchronous Calculus of Communicating Systems) [Mil83], which

extends CCS with primitives to encode synchrony. SCCS gave birth to other process calculi such as Meije [AB84]. Several *synchronous programming languages* have followed applying the synchronous approach. According to their programming style, synchronous languages can be classified into *imperative* and *declarative* languages. We survey the most representative ones of each class.

Synchronous imperative languages are inspired by classical imperative languages, i.e., in which the program structure reflects the order in which operations execute. They allow a modular description of reactive systems that require complex control structures. Esterel [BG92] has a textual syntax close to parallel programming languages such as ADA and Occam. It provides, in addition to the classical algorithmic control structures, concurrency primitives inspired by SCCS and Meije, as well as preemption structures. Argos [Mar91] is a graphical language, based on the Statecharts [Har87] formalism. An Argos program consists of hierarchical *Mealy machines*. These are finite-state automata in which outputs and next-state are both determined by the current-state and the current inputs.

Synchronous declarative languages are inspired by earlier studies on dataflow models [Kah74, McG82]. They allow the description of reactive systems that perform intensive data computation. Programs are described as networks of interconnected operators, evolving in parallel, and triggered by input arrivals. Lustre [HCRP91] is a functional language with textual syntax. A Lustre program is based on Mealy machines, the notion of state being implicit, unlike Argos. Signal [LGGLBLM91] is a relational language, defining relations between input and output flows (timed sequences of values), rather than simple functions as in Lustre. Contrarily to other synchronous languages, Signal programs are not necessarily deterministic. Each component induces its own constraints, which restrict the nondeterminism of the program. The Signal compiler is able to check the determinism of the conjunction of all constraints. This is the essence of the so-called multiclock or polychronous semantic model.

Causality problems in synchronous languages are either forbidden using static constraints (e.g., in Lustre) or resolved by the compilers using causality analysis algorithms. Examples of such algorithms are conditional dependence graph in Signal and computation of fixpoints in Esterel. Additionally, most synchronous languages are equipped with delay operators, which keep track of the values carried by expressions from one program step to the next. Based on how delay operators are used in a program, the compiler builds automatically an *internal state*.

Other proposals extend existing general-purpose languages with synchronous behaviour. Reactive-C provides a programming style similar to the C language. SynchCharts [And95] is a graphical language combining features from Esterel and Argos. Esterel-C (ECL) [LS99] and Java-Esterel (Jester) [AFFSV01] combine Esterel-like constructs with respectively C and Java languages. Lucid [WA85] is a higher-order functional language combining Lustre-like constructs and built upon Ocaml (Objective Caml) [LDG<sup>+</sup>03].

#### 2.2.2 Functional verification

Due to the massive use of synchronous systems in safety-critical environments, many analysis techniques have been exploited for synchronous systems encompassing automated test, model checking, SMT-Solving, and abstract interpretation. We focus here on the techniques related to our work, namely the verification by model checking. Functional properties that a synchronous system should satisfy fall into two classes: safety properties, expressing that something bad will never happen; and bounded liveness properties, which are timing properties expressing that something good will happen within a bounded future.

A convenient way to express properties is an application of [VW86], where the negation of a property is described by an automaton. The synchronous product of this automaton with the program ensures that no trace of the program is accepted by the automaton. Since almost all synchronous languages synthesise finite automata (e.g., Mealy machines) from programs and since the parallel composition in those languages is synchronous, properties can be expressed directly in the synchronous language. These properties, called *synchronous observers* [HLR93], are auxiliary programs which observe the inputs and outputs of the program under verification and decide whether it is correct.

Many software verification tools have been developed to model check synchronous systems. Xeve [Bou98] is a model checker for Esterel programs. The tool compiles synchronous programs into a finite state automaton over which properties such as deadlock and starvation absence can be checked. Lesar [HR99] is a model checker, which compiles a Lustre program into a finite state automaton and implements the verification by observers. Both model checkers interface with automata-based tools such as Auto and Autograph [RdS90]. In [MRBS01], Signal programs are verified by means of equation systems, thus avoiding state space enumeration. Properties such as invariance and reachability can be verified.

Model checking has been mainly used to verify properties depending only on logical dependence between events. Traversing the set of control states of a validation program can be either enumerative or symbolic. For properties involving numerical values, such as bounded liveness properties, abstract interpretation techniques are seemingly more appropriate [HPR97]. However general liveness properties involving unbounded future are rarely addressed in synchronous languages. Expressing such properties requires more expressive and complex formalisms such as temporal logics and Büchi automata.

# 2.3 The asynchronous approach

A reactive system is asynchronous if the time in which an event occurs and its duration are considered of less concern.

While the asynchronous approach deliberately abstracts from the precise timing of events, the order of some events (sequential composition) and their simultaneity can

be described. This way of modelling provides asynchronous models with simplicity and abstraction, making them appropriate for modelling distributed and concurrent systems.

## 2.3.1 Communication models

Communication mechanisms are required to enable interaction between concurrent components, as the time in which input and output events occur is unspecified. Existing communication mechanisms include shared memories and message-passing communication.

Shared memory communication, introduced by Dijkstra [Dij65], enables concurrent components to communicate by altering the contents of shared locations. Languages adopting this mechanism include Java and C#. The access of concurrent components to shared locations should be controlled, for example, by using *mutual exclusion* protocols. Well-known examples of such protocols are Peterson's and Dekker's protocols.

Message-passing enables concurrent components to communicate with each other by exchanging messages. Message exchange can be either *synchronous* or *asynchronous*.

Asynchronous message-passing takes arbitrary delay, i.e., the elapsed time between message emission and reception is abstracted away. This requires the introduction of buffers or *channels* as proposed by Dijkstra [Dij72] which serve to store messages before their transmission. As such, asynchronous message-passing does not force participant components to wait for each other to communicate. Message-passing channels has been adopted by specification languages for communication protocols, such as the ITU standard SDL [BHS91] and Promela [Hol91]. In Promela, channels store messages in first-in first-out order, by default. If synchronous communication is required, it can be modelled by setting the channel size to zero.

Synchronous message-passing requires messages emitted by a component to be received by other components at the same time instant. In the asynchronous abstraction of time, this requires the introduction of communication events, called synchronisation or rendezvous between the participant components. Synchronous message-passing is intended to be independent of the medium used to communicate. The communication medium, which may be a shared location, could itself be modelled as a subordinate component that synchronises with emitters and receivers. Synchronisation is blocking, i.e., it happens only when all participants are ready to communicate. As such, the emitter component blocks until message reception, after which the different components evolve independently. Beyond message exchange, (dataless) synchronisation can be used to express the simultaneity of specific events of concurrent components. Synchronous message-passing is the main interaction paradigm used in process algebras such as CCS [Mil89], CSP [Hoa85], ACP [BK85], and LOTOS [BB87].

Hiding and nondeterminism operators, which are specific to some asynchronous languages, provide behavioural descriptions with high abstraction capability. The hiding operator is essentially present in process algebra. It transforms events into *invisible* ones, i.e, event occurrence is neither detectable nor controllable by the environment. Synchronisation on invisible events is forbidden.

Nondeterminism is aimed at accurately disregarding irrelevant aspects of the actual system. Examples of situations in which nondeterminism is helpful are the following:

- Modelling concurrency by interleaving, thus abstracting from the speed of concurrent components.

- Abstracting from complex details of the physical environment.

- Abstracting from implementation details either because these are considered irrelevant or because the aim is to develop a simplified system meeting primary specifications before refining it to meet more detailed ones.

#### 2.3.2 Functional verification

State space exploration techniques, including reachability analysis and model checking, are the most widespread approaches for dealing with concurrent systems containing complex data structures. CADP [GLMS13] and Spin [Hol04] are seemingly the two oldest model checkers that are still actively maintained and that benefit from a worldwide user community. Both tools support on-the-fly techniques, which consist in constructing and exploring state spaces on demand, guided by the verification task instead of generating state spaces exhaustively and then performing verification. This provides a way to fight against state space explosion, essentially caused by asynchronous concurrency and complex data structures.

CADP supports several input specification languages, among which LNT [CCG<sup>+</sup>16], LOTOS and FSP [MK06]. They rely on an action-based semantic model; by considering systems whose behavioural semantics can be represented using labelled transition systems. Model checkers of CADP are based on branching-time logics, which are adequate with bisimulation reductions and compositional verification. More details about the CADP toolbox will follow in Section 2.4.

SPIN supports Promela as input language. Promela relies on a state-based semantic model and considers systems whose behavioural semantics can be represented using Kripke structures. Correctness properties can be specified as process invariants, using assertions, as LTL formulas, or as formal Büchi automata.

Among other well-known tools, CWB [CPS89] (Concurrency Workbench) deals with CCS process algebra. CWB-NC [CLS00] (Concurrency Workbench of the New Century) is the continuation of research started in the Concurrency Workbench project. FDR [GABR14] is a model checker for verifying systems modelled in CSP. The mCRL2 toolset [CGK<sup>+</sup>13] is based on a variant of the ACP process algebra equipped with abstract data types.

# 2.4 The CADP toolbox for the verification of asynchronous systems

CADP is a modular software toolbox implementing the results of concurrency theory in the context of asynchronous concurrent systems. Started in the mid 80s, CADP includes today more than 50 tools and code libraries, among which compilers for various formal specification languages, equivalence checkers, model checkers, compositional verification tools, and performance evaluation tools. We focus here on some salient features of the languages and tools related to our work and required to the comprehension of this thesis.

LNT (*Lotos New Technology*) [CCG<sup>+</sup>16] is a specification language derived from the ISO standard E-Lotos [ISO01]. The LNT.OPEN tool translates LNT specifications into LTSs, given in BCG (*Binary Coded Graphs*) file format, suitable for on-the-fly exploration. Section 2.4.2 presents informally a subset of the LNT language.

MCL (Model Checking Language) [MT08] is an expressive temporal logic, extending the alternation-free  $\mu$ -calculus [EC82] with generalised regular expressions, data-based constructs, and fairness operators. The EVALUATOR 4.0 model checker implements an efficient on-the-fly model checking procedure for MCL. It also exhibits full diagnostics (examples and counterexamples) as subgraphs of the LTS illustrating the truth value of MCL formulas. Section 2.4.3 presents informally a subset of the MCL language.

LTS minimisation is possible by using equivalence checking, which collapses the equivalent states in the LTS. Several equivalence relations are implemented in CADP, including strong [Par81], branching [vGW89, vGW96], and divergence-sensitive branching [vGW89, vGW96] bisimulation relations. A definition of those relations together with a formalisation of LTSs is given in Section 2.4.1.

SVL (Script Verification Language) [GL01, Lan02] is both a high-level scripting language proposed to CADP end-users and a compiler that translates SVL scripts into Bourne shell scripts. SVL enables to express complex verification scenarios, including property specification, LTS minimisation, abstraction, comparison, which orchestrates calls to the CADP tools.

#### 2.4.1 Labelled Transition Systems (LTS)

**Definition 2.1.** (Labelled transition system) An LTS is a quadruple  $(\mathbf{S}, \mathbf{L}, \rightarrow, s_0)$  where:

- **S** is a set of states.

- **L** is a set of labels.

- $\rightarrow \subseteq \mathbf{S} \times \mathbf{L} \times \mathbf{S}$  is the labelled transition relation.

- $-s_0 \in S$  is the initial state.

18

We write  $s \xrightarrow{\ell} s'$  as a shorthand for  $(s, \ell, s') \in \to$ . There exists a label, written  $\tau$  or i, called the *invisible label*, which denotes internal actions. All labels different from  $\tau$  are called the *visible* labels. An LTS is finite if its sets of states and transitions are both finite.

LTS equivalences Several equivalence relations between LTSs are available in the literature, differing mainly in the way they treat invisible labels. We focus on a few of them, namely strong bisimulation, branching bisimulation and its divergence-sensitive variant.

**Definition 2.2.** (Strong bisimulation) A strong bisimulation is a symmetric relation  $R \subseteq S \times S$  such that if  $(s_1, s_2) \in R$ , then for all  $s_1 \xrightarrow{a} s'_1$ :

- there exists  $s'_2$  such that  $s_2 \xrightarrow{a} s'_2$ , and

- $-(s_1', s_2') \in R.$

Two states  $s_1$  and  $s_2$  are strongly bisimilar if there exists a strong bisimulation R such that  $(s_1, s_2) \in R$ . Two LTSs are strongly bisimilar if their initial states are strongly bisimilar.

**Definition 2.3.** (Branching bisimulation) A branching bisimulation is a symmetric relation  $R \subseteq S \times S$  such that if  $(s_1, s_2) \in R$ , then for all  $s_1 \stackrel{a}{\to} s_1'$ :

- either  $a = \tau$  and  $(s'_1, s_2) \in R$ , or

- there exists a sequence  $s_2 \xrightarrow{\tau^*} s_2' \xrightarrow{a} s_2''$  such that  $(s_1, s_2') \in R$  and  $(s_1', s_2'') \in R$ .

Two states  $s_1$  and  $s_2$  are branching bisimilar if there exists a branching bisimulation R such that  $(s_1, s_2) \in R$ . Two LTSs are branching bisimilar if their initial states are branching bisimilar.

Branching bisimulation does not distinguish between inaction and a cycle of internal actions. Divergence-sensitive branching bisimulation (or divbranching bisimulation for short) is introduced to take into account cycles of internal actions.

**Definition 2.4.** (Divergence-sensitive branching bisimulation) A divbranching bisimulation is a branching bisimulation R such that if  $(s_1^0, s_2^0) \in R$  and there is an infinite sequence  $s_1^0 \stackrel{\tau}{\to} s_1^1 \stackrel{\tau}{\to} s_1^2 \stackrel{\tau}{\to} \dots$  with  $(s_1^i, s_2^0) \in R$  for all  $i \geq 0$ , then there is an infinite sequence  $s_2^0 \stackrel{\tau}{\to} s_2^1 \stackrel{\tau}{\to} s_2^2 \stackrel{\tau}{\to} \dots$  such that  $(s_1^i, s_2^i) \in R$  for all  $i, j \geq 0$ .

Two states  $s_1$  and  $s_2$  are divbranching bisimilar if there exists a divbranching bisimulation R such that  $(s_1, s_2) \in R$ . Two LTSs are divbranching bisimilar if their initial states are divbranching bisimilar.

## 2.4.2 The LNT language

The LNT formal language is rooted in a core powerful language, combining mainstream imperative and functional traits, which is smoothly extended with concurrency-related primitives. LNT is endowed with formal operational semantics defined in terms of LTSs (see [CCG<sup>+</sup>16] for a detailed presentation).

### Types, statements, and functions

LNT provides constructed data types, statements built upon standard algorithmic control structures, and functions.

**Types** LNT types encompass basic types such as Boolean, integers, floating-point numbers, and character strings, as well as user-defined (possibly unbounded) data types such as records, unions, lists, sets, and arrays. The following is an example which defines a simple enumerated LNT data type temperature:

```

1 type temperature is

2 low, normal, high, very_high

3 with "!=", "==", "<", "<=", ">=", ">=", ">="

4 end type

```

The "with" clause specifies the predefined functions for type temperature.

**Statements** LNT statements build upon standard algorithmic control structures, such as variable assignment, sequential composition, conditional (**if-then-else**), pattern matching (**case**) statements, and loops (**for**, **while**). In particular, statement "**var** X: T **in** I **end var**" declares variable X of type T in the scope of statement I. Hence, LNT dissociates between variable declarations (between the keywords **var** and **end var**) and variable modifications (inside I).

The following is an example of a statement which declares a variable, to which it assigns a value.

Functions LNT functions can have in parameters (call by value), out parameters (call by reference, the function being in charge of producing a value for the parameter), and "in out" (call by reference, the function being allowed to read and update the parameter value). Actual parameters are preceded by symbols "!", "?", and "!?", respectively. Functions are deterministic and execute atomically without producing transitions in the generated LTS.

The following is an example of a function *check\_temperature* reading the ambient temperature and raising an alarm if the temperature is high:

```

function check_temperature (in ambient: temperature, out alarm: bool) is

if (ambient >= high) then

alarm := true

else

alarm := false

end if

end function

```

The following is an example combining a call to the function *check\_temperature*, with the **var** operator and variable assignment.

```

var ambient: temperature, alarm: bool in

ambient := normal;

eval check_temperature (ambient, ?alarm)

end var

```

Note that LNT types, statements, and functions look similar to mainstream programming languages, which favours the acceptance of the language by users compared to classical process algebras.

# Behaviours and processes

Processes include functions, with the addition of gates, which are used for communication, and other behaviours built upon gates and process algebraic operators, including nondeterministic statements and parallel composition.

**Nondeterministic assignment** The behaviour "X :=any T [where V ]" assigns to the variable X an arbitrary value of type T. The optional where clause with a Boolean expression V, supposed to use X, enables to express Boolean constraints on the possible values.

Nondeterministic choice The behaviour select  $B_1$  [] ... []  $B_n$  end select may execute either  $B_1$ , ..., or  $B_n$ .